## FIXED-POLE ACTIVE PI FILTER DESIGN FOR HIGH FREQUENCY NONLINEAR PLL MODELS

### S.J. Abu Bakar, N.S. Ahmad and P. Goh

School of Electrical and Electronic Engineering, Engineering Campus, Universiti Sains Malaysia, 14300 Penang, Malaysia.

Corresponding Author's Email: syazreen@usm.my

Article History: Received 7 December 2018; Revised 10 April 2019; Accepted 8 August 2019

**ABSTRACT:** A Phase-locked loop (PLL) is a basic control system that attempts to produce an output waveform that can match with the input reference signal in the shortest time possible. A filter is one of the main components in the PLL blocks, and it plays a very important role to determine the range of input frequency that can ensure the system stays in a locked condition. This paper focuses on designing a fixed-pole active PI filter which is suitable for high-frequency PLL-based circuits such as those used in clock generators. As PLL is bound to fall out of lock due to the nonlinear effects from its phase detector, a new approach is introduced in this work which is to combine the linear and nonlinear control method to ensure stability. Having had the phase margin specified a priori, it is shown by simulation that the allowable range of input frequency such that the system remains locked can be expanded.

KEYWORDS: Nonlinear PLL; Active PI Filter; Phase Margin

## 1.0 INTRODUCTION

The basic function of a PLL system is to ensure that the phase and frequency of the output signal are equivalent to those of the input signal. The PLL system is fundamental to many electronic circuits used for frequency control such as clock synchronization and distribution [1]. It is also commonly used in a telecommunication system for modulation/ demodulation and frequency synthesizer [2-3]. With the technology advancement in the electronic system, advanced development of the PLL circuit was successfully implemented on a single integrated chip (IC) back in the year 1965 [4]. Since then, the demand for this type of IC design with higher performance captures the attention of many researchers [5-6]. The PLLs have also been used for high-frequency application [7-9] which include clock generators for microprocessors of which the operation frequencies start at 100MHz and above [10].

The PLL structure usually consists of a phase detector (PD), loop filter (LF), and voltage controlled oscillator (VCO) [11]. Each of these blocks has an important role to ensure the system functions accurately according to the desired specifications. The performance of the PLL system which is usually indicated by the locking range and settling time also depends on the parameters of the filter [12]. Three basic filter types mostly used in PLL design are passive, active and proportional integral (PI) filters. Another important parameter that can be considered in the filter design is phase margin. Few studies which discuss the impact of the phase margin on loop response can be found in [13-15].

As most PLL systems are nonlinear due to the effects from the PD and VCO [16–19], extensive studies regarding their stability and working frequency range have been carried out since the past few decades [20–23]. These include classical graphical techniques [20], LaSalle theorem [21] and Lyapunov redesign [22]. For nonlinearities that can be categorized as sector- and slope-bounded, the circle and Popov criteria can provide sufficient stability conditions for the closed-loop systems under certain assumptions [23].

In this paper, an alternative method is proposed to design a fixed-pole second order active PI filter for nonlinear PLL by combining linear and nonlinear design approaches. In this new method, we use the  $H_{-\infty}$  control technique where the phase margin is specified a priori. The performance of the nonlinear PLL system in terms of locking range and locking time is then compared with the filter designed when the phase margin is allowed to take any values.

## 2.0 METHODOLOGY

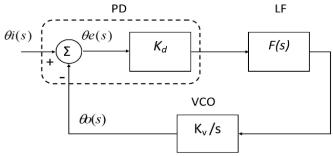

Assuming all high frequency components have been attenuated, the resulting block diagram of PLL in phase domain can be illustrated in Figure 1.

Figure 1: General block diagram for a linear PLL model in phase domain [24]

The transfer function of the closed-loop PLL without considering nonlinearity can be written as:

$$G(s) = \frac{K_d K_v F(s)}{s + K_d K_v F(s)} \tag{1}$$

where the  $K_d$  and  $K_v$  is the PD gain (volts/rad) and VCO gain (rad/volt second) respectively. Whereas F(s) is the filter's transfer function which takes the form:

$$F(s) = \frac{K_0 s^2 + K_1 s + K_2}{s^2}$$

(2)

which is also known as fixed-pole active PI filter. To ensure the stability of the PLL system in the linear region, sufficient gain or phase margins must be preserved. The phase margin $\emptyset_m$  (in degree) can be determined by the parameter  $\gamma$  as follows [25]:

$$\left|\frac{H(s)}{1+H(s)}\right| < \gamma \tag{3}$$

where H(s) is the open loop transfer function of the PLL system. The useful relationship between phase margin  $\emptyset_{m}$  and  $\gamma$  can be approximated by the following equation:

$$\gamma \approx \frac{1}{2\sin(0.5\phi_m)} \tag{4}$$

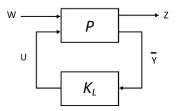

The closed-loop system in Figure 1 can be restructured into Figure 2, with the state space system P written as:

$$\dot{x} = A_a x + B_1 w + B_2 u$$

$$z = C_1 x$$

$$y = C_2 x$$

$$(5)$$

and the state space of the filter given by:

$$u = K_L x \tag{6}$$

with notation that  $C = \begin{bmatrix} C_1 & C_2 \end{bmatrix}^T = \begin{bmatrix} 1 & 0 \end{bmatrix}^T$  and z = u.

The resulting closed-loop system becomes:

$$M \sim \begin{bmatrix} A_a + B_2 K_L & B_1 \\ K_L & 0 \end{bmatrix}$$

(7)

which is suitable for  $H_{\infty}$  synthesis framework.

Figure 2: General block diagram for H<sub>∞</sub> synthesis

The following method can then be applied:

#### **Lemma 1:** $H_{\infty}$ approach [25].

Given an LTI system  $\widetilde{M}(s) = C(sI - A)^{-1}B + D$ . Then the following statements are equivalent:

- i. *A* is Hurwitz stable and  $\|\widetilde{M}(s)\|_{\infty} < \gamma$ .

- ii. There exists a positive definite matrix  $P = P^T$  such that the following LMI hold.

$$\begin{bmatrix} A^T P + PA & PB_1 & C^T \\ B_1^T P & -\gamma I & D^T \\ C & D & -\gamma I \end{bmatrix} \le 0$$

(8)

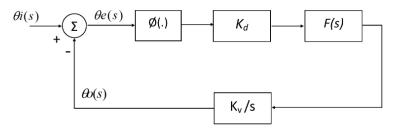

In order to ensure stability of the PLL when it is subjected to the nonlinear effect from the PD, the nonlinear function needs to be included as shown in Figure 3. It is then straightforward to rearrange the loop into the so-called Lur'e system [26] which is suitable for application of the circle criterion. Assuming the nonlinearity  $\phi(y)$  is static, memoryless, and it satisfies the sector bounded as described by:

$$0 \le \frac{\phi(y)}{y} \le K, \quad \forall y \ne 0 \tag{9}$$

The following criterion can be applied:

#### Lemma 2: Circle Criterion [27].

Consider the system in Figure 3 and define  $\tilde{M} = K_d K_v F(s)/s = C(sI - A)^{-1}B + D$ , and  $\emptyset$  satisfying the sector given by Equation (8). The closed-loop system is absolutely stable if A is Hurwitz and the  $\tilde{M}(s)$  lies on the right-half plane of the Nyquist plot defined of Re[s] = -1/K such as

$$Re[1 + K\widetilde{M}(j\omega)] > 0, \quad \forall \omega \in \mathbb{R}$$

(10)

By using Kalman-Yakubovich-Popov (KYP) Lemma [28], the frequency domain from the Equation (10) can be transformed into an LMI form given by:

$$\begin{bmatrix} A^T P + PA & PB - C^T \\ B^T P - C & -2\tilde{K}^{-1} \end{bmatrix} \le 0$$

(11)

By integrating Lemmas 1 and 2, the proposal of a method to design the filter as follows:

**Proposed method**: Consider the fixed-pole an active PI filter as in Equation (2) and let  $K_1 = [K_0 K_1 K_2]$ . Given  $\gamma > 0$ , if Equations (12)-(14) are feasible,

$$X > 0, \tag{12}$$

$$\begin{bmatrix} \boldsymbol{X}\boldsymbol{A}_{a}^{T} + \boldsymbol{W}^{T}\boldsymbol{B}_{2}^{T} + \boldsymbol{A}_{a}\boldsymbol{X} + \boldsymbol{B}_{2}\boldsymbol{W} & \boldsymbol{B}_{1} - \boldsymbol{W}^{T} \\ \boldsymbol{B}_{1}^{T} - \boldsymbol{W} & -2\widetilde{K}^{-1} \end{bmatrix} \leq 0,$$

(13)

$$\begin{bmatrix} \mathbf{X}A_a^{\ T} + \mathbf{W}^T B_2^{\ T} + A_a \mathbf{X} + B_2 \mathbf{W} & B_1 & \mathbf{W}^T \\ B_1^{\ T} & -\gamma I & 0 \\ \mathbf{W} & 0 & -\gamma I \end{bmatrix} \le 0$$

(14)

then the filter can be obtained by  $K_L = WX^{-1}$ .

*Proof*: Perform congruence transformation by pre- and post-multiplying of inequality Equation (13) by T=diag( $X^{-1}$ ,I), and Equation (14) by T=diag( $X^{-1}$ ,I,I), where X=P<sup>-1</sup>, with a change of variable W=K<sub>1</sub>X, Equations (10) and (11) is obtained respectively.

*Remark* 1: Without specifying  $\gamma$  a priori, an optimal filter may be obtained if Equations (12)-(14) are feasible by minimizing the parameter. In this case, we denote the method as method 1 for comparisons in the simulation results section.

### 3.0 SIMULATION RESULTS

The simulation of nonlinear PLL system is analyzed in phase domain model as shown in Figure 3. The nonlinearities from the PD can be characterized by a sine-wave or a triangular-wave such as

$$\phi(.) = \sin(\theta_e) \tag{15}$$

for the sine-wave; and for the triangular-wave [29].

$$\phi(.) = \frac{4}{\pi} \sum_{n=0}^{5} \frac{(-1)^n}{(2n+1)^2} \sin[(2n+1)\theta_e]$$

(16)

Figure 3: Nonlinear PLL system in phase domain

By setting the VCO gain,  $K_v$ =1, and PD gain,  $K_d$ =1, the parameters of the second order active PI filter obtained by using proposed method are given in Table 1. The results are compared with the designed filter via method 1.

| Table 1. Second order milers' structure |                                                                                  |  |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------|--|--|--|

| Method                                  | Filter, F(s)                                                                     |  |  |  |

| Proposed Method                         | $\frac{4.088 \times 10^{10} s^2 + 1.444 \times 10^8 s + 2.924 \times 10^5}{s^2}$ |  |  |  |

| Method 1                                | $\frac{2.689 \times 10^8 s^2 + 3.639 \times 10^6 s + 3.133 \times 10^4}{s^2}$    |  |  |  |

Table 1: Second order filters' structure

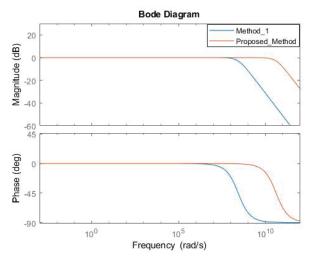

Figure 4 shows the bode plot for linear PLL with designed filter via the proposed method and method 1. The plotted graph shows the closed-loop response of the PLL system at phase margin of 60°, which  $\gamma$  equivalent to one.

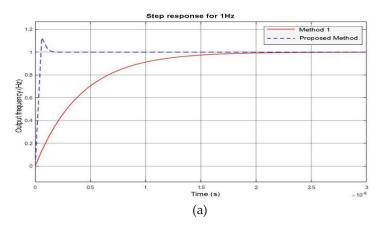

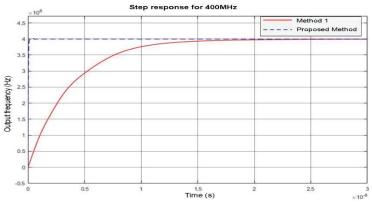

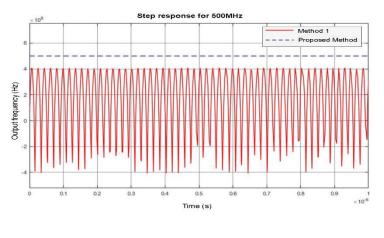

The simulation results for step response (1Hz, 400MHz, and 500MHz) of the nonlinear PLL system with the designed filter via the proposed method and method 1 are shown in Figure 5. From the figure, at low input frequency of 1Hz, the step response for designed filter via the proposed method produced small overshoot. However, when the frequency was higher, no overshoot was observed. When the frequency was increased to 500MHz, it showed that the designed filter via method 1 failed to track the input, while the designed filter via the proposed

method remained locked. From the same graph, it can be easily seen that the steady state response for the designed filter via proposed method is much faster than method 1.

Figure 4: Bode plot for closed-loop linear PLL system with designed filter via the proposed method and method 1

The locking range and settling time for the designed filter via the proposed method and method 1 are summarized in Table 2. The results are also compared with the nonlinearity from the sine-wave and triangular-wave PD. From the tabulated table, the locking range for the PLL system with the designed filter via the proposed method for both types of nonlinearities is larger than method 1. However, the settling times for both the designed filter via the proposed method and method 1 with sine-wave PD are much faster than the triangular-wave PD.

Table 2: The locking range( $\omega_L$ ) and settling time (t<sub>s</sub>) for nonlinear PLL system using triangular and sine-wave PDs for the proposed method and method 1

| una metroa 1    |                 |                        |                    |                        |  |

|-----------------|-----------------|------------------------|--------------------|------------------------|--|

| Performance     | Sine-wave PD    |                        | Triangular-wave PD |                        |  |

|                 | $\omega_L(MHz)$ | $t_s(s)$               | $\omega_L(MHz)$    | $t_s(s)$               |  |

| Proposed method | 40000           | 0.6 X 10 <sup>-8</sup> | 60000              | 1.2 X 10-8             |  |

| Method 1        | 200             | 3.0 X 10-8             | 400                | 3.8 X 10 <sup>-8</sup> |  |

(c)

Figure 5: Step response for nonlinear PLL system with designed filter via proposed method and method 1 at frequencies (a) 1Hz, (b) 400MHz and (c) 500MHz using triangular-wave PD

# 4.0 CONCLUSION

In this paper, a new technique to design a fixed-pole active PI filter for nonlinear PLL system is presented. Based on the simulation results, the designed filter via the proposed method offers more advantages in terms of locking range and settling time as compared to method 1. This type of filter design is suitable for clock generator on electronic board application, which requires a frequency range of 100MHz and beyond. For future work, other values of phase margins can be considered to satisfy the PLL design for other types of applications with different performance specifications.

# ACKNOWLEGMENT

The authors would like to acknowledge the financial support by the Ministry of Education of Malaysia under the FRGS Scheme with reference number 203/PELECT/6071267.

## REFERENCES

- [1] A.Gameiro, "An Extended Phase-Locked Loop for Clock Synchronization Applications," in Global Telecommunications Conference, San Francisco, USA, 1994, pp. 956–961.

- [2] S. Stevanovic and B. Pervan, "A GPS phase-locked loop performance metric based on the phase discriminator output," *Sensors*, vol. 18, no. 1, pp. 1-23, 2018.

- [3] G. Bhargav, G. Prasad, S.D. Canchi, and B. Chanikya, "Design and analysis of phase locked loop in 90nm CMOS," in 13<sup>th</sup> International Conference on Wireless and Optical Communications Networks (WOCN), Hyderabad, Telangana State, India, 2016, pp. 1–7.

- [4] A. Grebene and H. Camenzind, "Phase locking as a new approach for tuned integrated circuits," in IEEE International Solid-State Circuits Conference. Digest of Technical Papers, Philadelphia, USA, 1969, pp. 100–101.

- [5] A.B. Gregene. and H.R. Camenzind, "Frequency-selective integrated circuits using phase-lock techniques," *IEEE Journal of Solid-State Circuits*, vol. 4, no. 4, pp. 216–225, 1969.

- [6] B. Razavi, Monolithic Phase-Locked Loops and Clock Recovery Circuits: Theory and Design. New Jersey: John Wiley & Sons, 1996.

- [7] B.K. Mishra, S. Save and S. Patil, "Design and Analysis of Second and Third Order PLL at 450MHz," *International Journal of VLSI Design and Communication Syststem*, vol. 2, no. 1, pp. 97–114, 2011.

- [8] E. Ozeren, S. Zihir, F. Tasdemir, I. Tekin and Y. Gurbuz, "A Fully Integrated Multiband Frequency Synthesizer for WLAN and WiMAX applications," in the 5<sup>th</sup> European Microwave Integrated Circuits Conference, Paris, France, 2010, pp. 369–372.

- [9] V. Valenta, M. Villegas and G. Baudoin, "Analysis of a PLL Based Frequency Synthesizer using Switched Loop Bandwidth for Mobile WiMAX," in 18<sup>th</sup> International Conference Radioelektronika, Prague, Czech Republic, 2008, pp. 1–4.

- [10] I.A. Young, J.K. Greason and K.L. Wong, "A PLL clock generator with 5 to 110 MHz of lock range for microprocessors," *IEEE Journal of Solid-State Circuits*, vol. 27, no. 11, pp. 1599-1607, 1992.

- [11] F.M. Gardner, *Phaselock Techniques*. New York: John Wiley & Sons, 2005.

- [12] R.E. Best, *Phase-Locked Loops: Design, Simulation, and Application*. New York: McGraw-Hill, 2007.

- [13] K. Kishine, K. Fujimoto, S. Kusanagi and H. Ichino, "PLL design technique by a loop-trajectory analysis taking decision-circuit phase margin into account for over-10-Gb/s clock and data recovery circuits," *IEEE Journal Solid-State Circuits*, vol. 39, no. 5, pp. 740–750, 2004.

- [14] K. Kalita and T. Bezboruah, "Impact of gamma optimization parameters and phase margin on closed loop gain of phase-locked loop," *International Journal of Electronics and Communication Engineering*, vol. 6, no. 3, pp. 225–231, 2013.

- [15] N.A. Anang, Z. Jamaludin, L. Abdullah, M. Maharof and M.H. Nordin, "Robust Motion Controller Design for Precise Tracking of Ball Screw Driven Positioning System," *Journal of Advanced Manufacturing Technology*, vol. 12, no. 1(4), pp. 73-85, 2018.

- [16] B. Daniels and R. Farrell, "Nonlinear Analysis of the 2<sup>nd</sup> Order Digital Phase Locked loop," in IET Irish Signals and Systems Conference, NUI, Galway, 2008, pp. 66-71.

- [17] G.A. Leonov and N.V. Kuznetsov, Nonlinear Mathematical Models of Phase-Locked Loops, Stability and Oscillations (Stability Oscillations and Optimization of Systems). UK: Cambridge Scientific Publishers, 2014.

- [18] N. Margaris and P. Mastorocostas, "On the Nonlinear Behavior of the Analog Phase-Locked Loop:Synchronization," *IEEE Transaction on Industrial Electronics*, vol. 43, no. 6, pp. 621–629, 1996.

- [19] B.C. Sarkar, S.S. De Sarkar and T. Banerjee, "Nonlinear dynamics of a class of symmetric lock range DPLLs with an additional derivative control," *Signal Processing*, vol. 94, pp. 631–641, 2014.

- [20] A.J. Viterbi, Principles of coherent communications. New York: McGraw-Hill, 1966.

- [21] J. LaSalle and S. Lefschetz, *Stability by Liapunov's direct method with applications*. New York: Academic Press, 1961.

- [22] D.Y. Abramovitch, "Lyapunov Redesign of Analog Phase-Lock Loops," IEEE Transaction on Communications, vol. 38, no. 12, pp. 2197–2202, 1990.

- [23] N.E. Wu, "Circle/Popov Criteria in Phaselock Loop Design," in Proceedings of the American Control Conference, Philadelphia, Pennsylvania, 1998, pp. 3226–3228.

- [24] D. Abramovitch, "Phase-Locked Loops: A Control Centric Tutorial," in Proceedings of the American Control Conference, Anchorage, USA, 2002, pp. 1–15.

- [25] K. Zhou and J.C. Doyle, *Essentials of robust control*. New Jersey: Prentice Hall Upper, 1998.

- [26] A.I. Lur'e and V.N. Postnikov, "On the theory of stability of control systems," *Appllied Mathematics and Mechanics*, vol. 8, no. 3, pp. 246–248, 1944.

- [27] J.C. Hsu, and A.U. Meyer, Modern control principles and applications. New York: McGraw-Hill, 1968.

- [28] A. Rantzer, "On the Kalman-Yakubovich-Popov lemma," *Systems and Control Letters*, vol. 28, no. 1, pp. 7–10, 1996.

- [29] W. Tranter, T. Bose and R. Thamvichai, "Basic Simulation Models of Phase Tracking Devices Using MATLAB," *Synthesis Lectures on Communications*, vol. 4, no. 1, pp. 1-136, 2010.